某设计,用户接口数据传输速率为10Gbps,每8个字节的数据对应一次查表需求,数据表存储在由DDR4 SDRAM组成的存储器中。工程师需综合考虑各方面要求,进行存储器的选型。

以下是选型时最关键的两个因素:

(1)产品对存储器容量的要求。

一般由系统设计部门和软件设计部门,根据产品需求,共同确定对存储器容量的要求。本案例中的数据表将被复制到存储器中,根据数据表的大小,可确定存储器存储容量。

(2)产品对存储性能的要求。

存储性能受DRAM数据传输速率、延时的影响。在项目前期,一般也是由系统设计部门与软件设计部门共同确定存储器需运行的速率。本案例中,初步确定存储系统由8Gb容量、速率2400Mbps的DDR4 SDRAM组成。

【讨论】

以下从硬件设计的角度,重点分析如何细化存储器的选型工作。

(1)确定存储器的数据位宽。

满足条件的DDR4有三种不同的数据位宽:4、8、16。数据位宽指一片DRAM芯片的数据信号线数目,例如,16位数据位宽的DRAM,其数据信号线为DQ[0:15],共16根。

数据位宽越宽的型号,在和CPU接口时,需使用的芯片数量越少,电路设计越简单。但根据第4章分析可知,其延时也将越大,访问效率将受到一定影响。所以,在这一步,硬件工程师需结合产品要求进行选型,且优先考虑访问效率。

在本案例中,为讨论简单起见,不考虑在有效数据段之间插入的闲置数据和编码产生的冗余数据等,则在最坏情况下,每秒钟需对存储器进行10Gb÷64b=156M次访问。根据表4.3,对8Gb容量存储器,只有选择8位数据或4位数据位宽的型号:才能满足本案例对访问效率的要求。为便于设计简单,本案例选择8位数据位宽的型号。

(2)确定CPU是否支持所选择的存储器。

在CPU手册中找到以下描述:The supported DRAM chip data width is x8 and supportedDRAM chip densities of 4Gb,8Gb and 16Gb。其含义是,该CPU只支持8位数据位宽的DRAM,且DRAM芯片容量应为4Gb、8Gb或16Gb。本案例所选择的DRAM芯片满足该要求。

(3)若选择双内核(TwinDie)的DRAM芯片需注意的问题。

在推出每一代芯片的大容量型号时,有时厂家会首先推出双内核版本的型号,以率先满足客户的需求。例如,一颗8Gb容量的芯片,片内实际可能采用的是两颗4Gb容量的内核。

若使用了双内核芯片,需注意存在两种情况:一种是该芯片为单Rank(SingleRank),另一种是该芯片为双Rank(Dual Rank)。

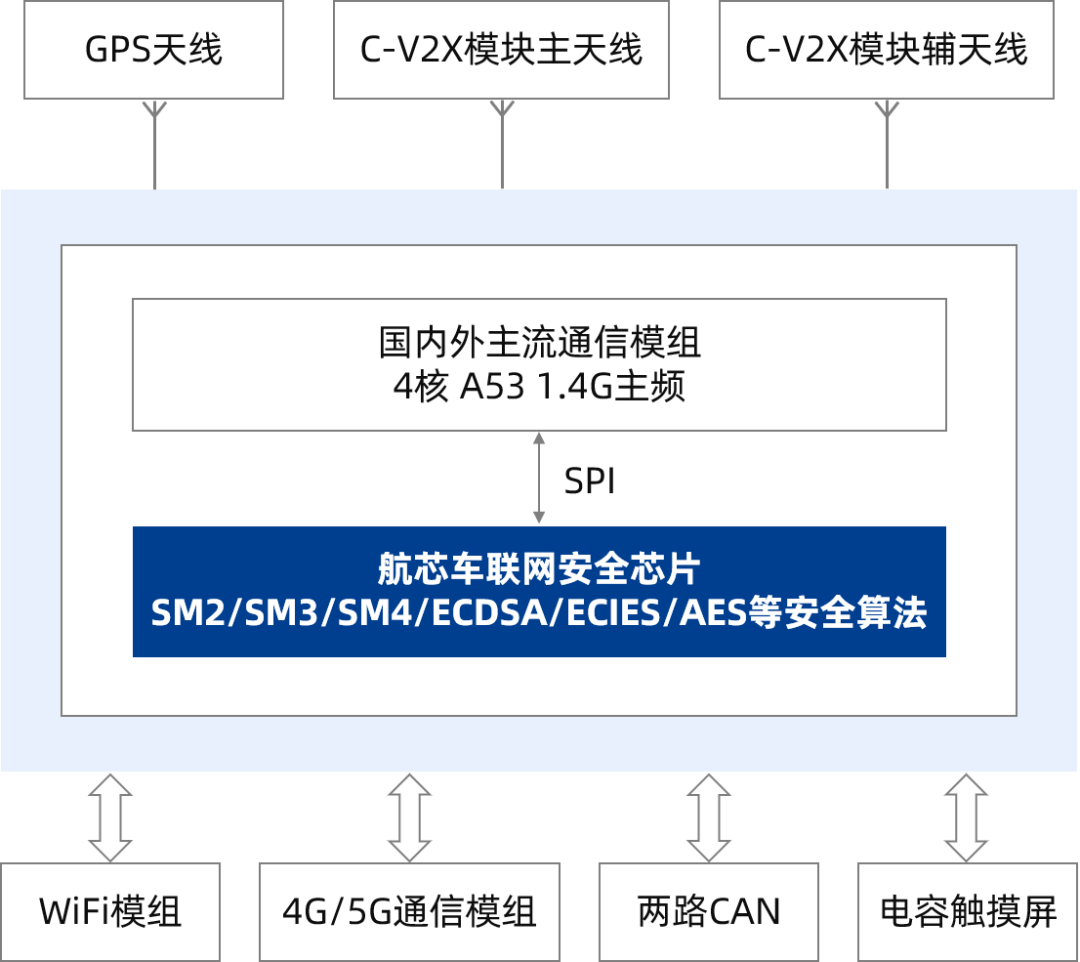

单Rank的双内核芯片和普通的单内核芯片的电路设计方式是相同的;双Rank的芯片比普通单内核芯片多一套CS_n、CKE、ODT控制信号线,如图5.5的CS1#、CKE1、ODT1所示。在选型时,必须核对CPU是否支持这第二套控制信号线,若不支持,则无法使用这类芯片。

随着技术的发展,对大容量的型号,厂家也会逐步停产双内核芯片,而改为推出大容量的单内核芯片。所以,在研发阶段,可以在原理图及PCB设计上做好兼容性设计,调试阶段采用双内核芯片,批量生产时,一旦厂家推出大容量单内核芯片,则在BOM(物料清单)中做元器件替代即可。

另外,若选择双Rank的双内核芯片,在布线设计时,需注意使CS_n、CKE、ODT的走线长度比其他地址控制信号线长一些。原因在于,芯片内部存在两个内核,因此对于这个芯片而言,地址控制信号实际上要接两个负载,但CS_n、CKE、ODT这几个信号,由于分成了两组,所以对于芯片而言,每个信号实际上只接一个负载,负载数目比其他地址控制信号少,导致负载容性偏小,为了满足等延时的要求,这几个信号的走线长度需比其他地址控制信号略长一些。至于需增长多少,可以利用芯片的IBIS模型结合封装模型进行仿真,也可以根据经验粗略估计。如芯片模型中CKE的容性为0.35pF,则可以粗略估计对50Ω阻抗的信号线CKE,需增加长度100mil左右。

(4)底层驱动程序的参数设置需和芯片的选型一致。

一般而言,DRAM芯片的位宽、内核数量、Bank地址/行地址/列地址数目等信息,对上层软件是透明的,但需要在底层驱动程序中正确地设置这些信息。所以,选型完成后,硬件工程师需将这些信息整理并提供给底层驱动工程师,辅助他们完成这些参数的设置。

以上案例来自电路设计领域知名专家-王老师《高速电路设计进阶》著作内容其一案例!